Breakthrough Semiconductor ReRAM Technology

CrossBar is advancing the frontier of memory and silicon systems, building architectures that combine performance, security, and verifiability at the hardware level.

Our Technology

ReRAM

Purpose-built memory and silicon architectures engineered for performance, security, and hardware-level verifiability.

Hardware Wallets

Open-source from chip RTL to application layer. IRIS-inspectable silicon, verifiable firmware. No closed components.

Seedless key management on a secure element. 10x faster than cloud-based MPC. Local threshold signing with no cloud dependency.

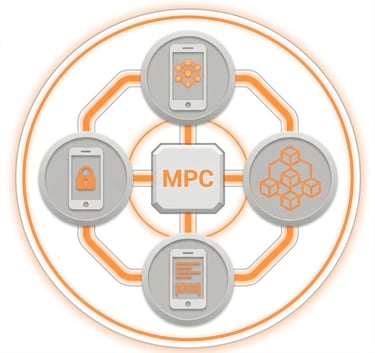

MPC

Why ReRAM is Fundamental

Traditional flash memory was designed for data storage, not for safeguarding cryptographic secrets. ReRAM changes the physics of what is possible.

200+

IP_PORTFOLIO

Patents Worldwide

ReRAM Process Node

Retention @ 100°C

Open-Source Stack

22nm

PROCESS_NODE

DATA_RETENTION

TRANSPARENCY

150yr

100%

High Density

Terabyte-scale on-chip storage with minimal layout overhead. Ultra-dense, stackable 3D cross-point arrays.

Energy Efficient

5× less energy than eFlash, 20× less than NAND, 30× less than SPI Flash, and 40× less than BLE.

High Performance

20ns read, 12μs write, no erase latency. 100× faster reads, and 1,000× faster writes than traditional memory.

Enhanced Security

Tamper-resistant storage for cryptographic keys. Prevents extraction and supports secure keys.

ReRAM Highlights

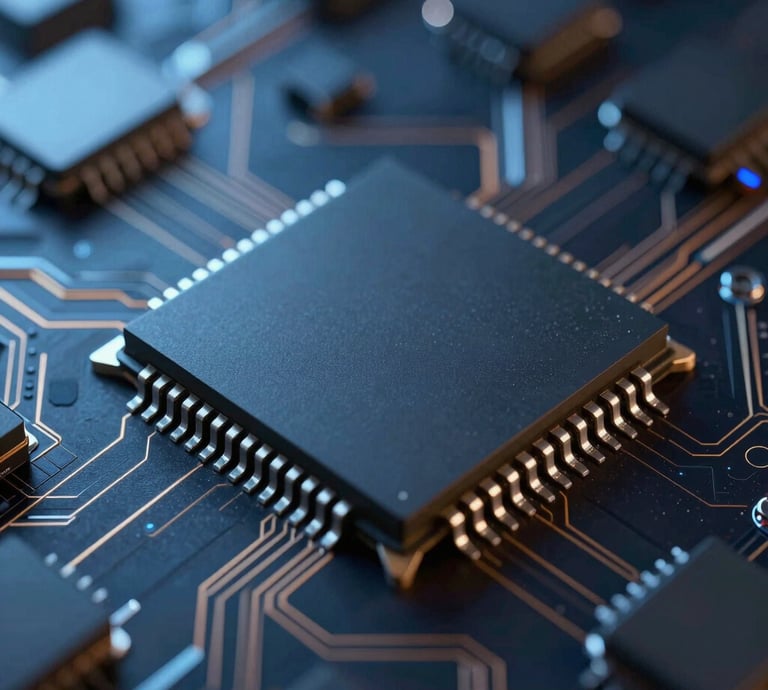

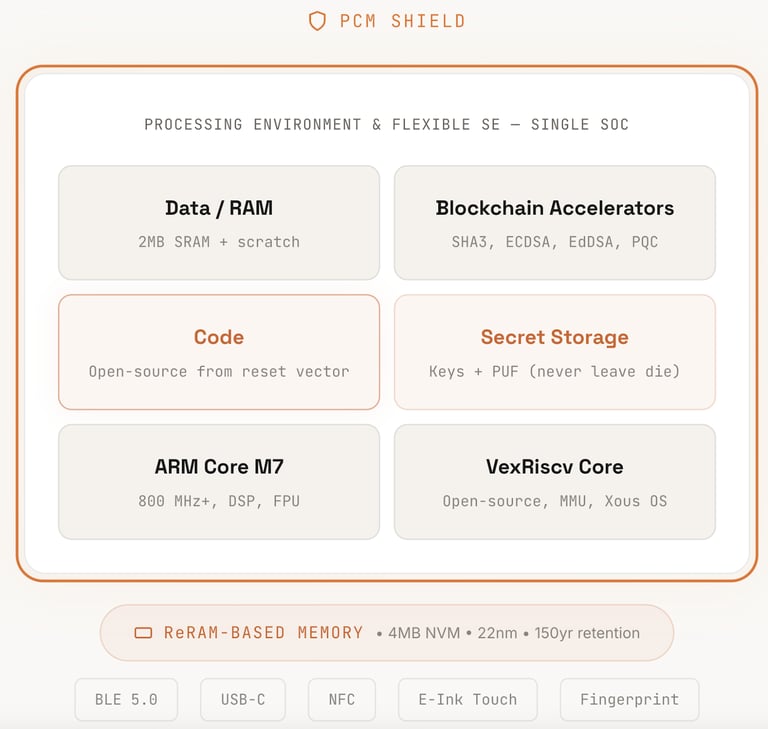

World's First Secure Processing Unit (SPU)

Innovative products leveraging crossbar architecture for secure computing.

DARIC SPU

DARIC is CrossBar’s purpose-built secure processing unit, combining compute, cryptographic acceleration, and ReRAM-based memory into a single monolithic architecture. Designed from the ground up for security and performance, it eliminates the need for fragmented systems and exposed interconnects.

Built on advanced-node ReRAM, DARIC enables physically secure key storage, high-speed execution, and long-term data integrity within one unified chip.

Integrated ReRAM for secure, high-retention memory

On-chip cryptographic engine (ECDSA, SHA, PQC-ready)

Monolithic design reduces attack surface

Open architecture for verifiability and auditability

// FLAGSHIP SECURITY CHIP

Sovrency Wallet

Multi-Party Computation moves key management from a single secret to a distributed protocol. CrossBar's E-MPC is the first implementation that runs entirely on a secure element — no cloud required.

No seed phrase or single point of compromise

Local, device-based MPC signing

Flexible threshold configuration (T-of-N)

Built on DARIC secure processing architecture

Seedless. Local. Sovereign.

// MPC POWERED PRODUCT

“If you can’t verify it, you don’t own it.”

Every layer verifiable. Every line auditable. From silicon to firmware — CrossBar is building the hardware foundation the open-source community has been waiting for.

// OPEN SOURCE HARDWARE

CrossBar is advancing the frontier of modern computing through memory and silicon innovation. We design high-performance, secure, and verifiable hardware systems that push beyond traditional architectures. We collaborate with engineers, researchers, and builders working at the edge of hardware, systems, and applied technologies.

Connect with CrossBar

// SILICON VALLEY HQ