## Cressbar

# Hyperconverged Infrastructure Virtualization

# **Delivering IGIOPS Per Server**

Sylvain Dubois

Vice President of Strategic Marketing and Business Development

Crossbar

#ARMTechCon

# Data centers going towards higher integration

# Storage Storage Storage W Hypervisor + Networking + Networking + Networking + Networking + Storage Hyper-Converged

### HYPERCONVERGED

2

### **"40% of enterprises use hyperconverged** units as a standard building block in the data center,

climbing rapidly over the next two years" 451 Research – Voice of the Enterprise

"The market for hyperconverged integrated systems (HCIS) will grow 79% to reach almost \$2 billion in 2016, propelling it toward mainstream use in the next five years"

Gartner, Inc.

### #ARMTechCon **Cressbar**

TRADITIONAL

# Promises and pain points of hyper-convergence infrastructure

#ARMTechCon **Cresbar**

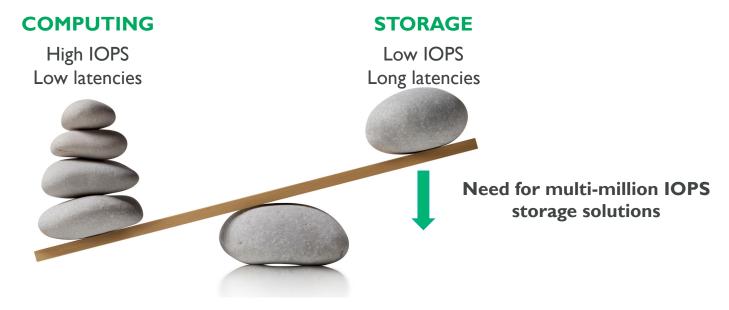

# Current NVM challenges in hyper-convergence

Current performance bottleneck is on storage side

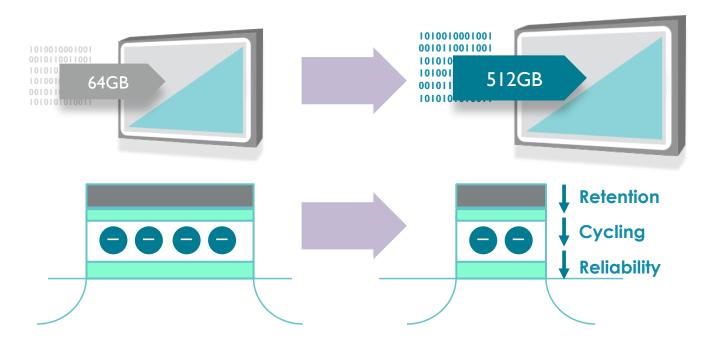

# NAND Flash NVM technology running out of steam

Electron-based storage facing scaling challenges with performance degradation

5

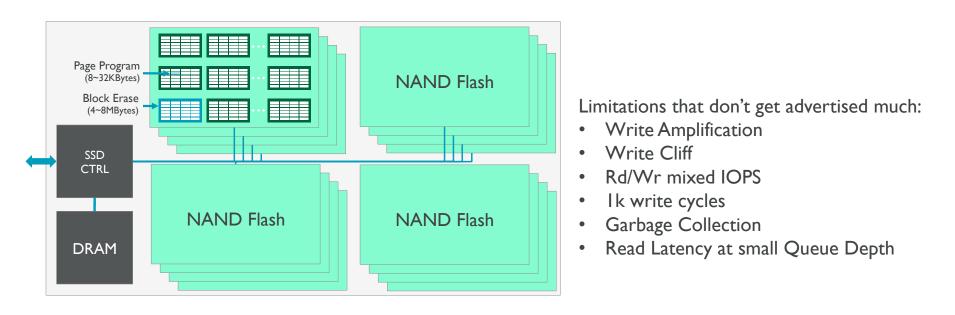

# Flash limitations getting harder to hide in SSDs

Fresh Out-of-Box performance is not representative of performance under constant load

#ARMTechCon **Cressbar**

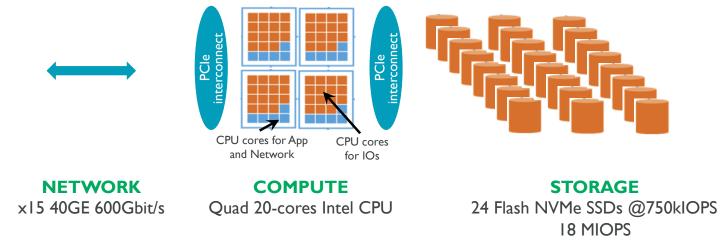

# Poor system efficiency in existing infrastructure

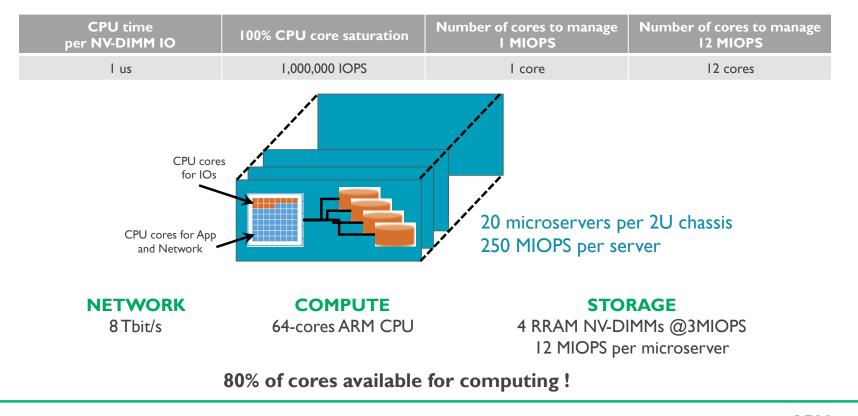

| CPU time per NVMe IO |        | 100% CPU core<br>saturation | Number of cores to<br>manage   MIOPS | Number of cores to manage 18 MIOPS |

|----------------------|--------|-----------------------------|--------------------------------------|------------------------------------|

| 10,000 CPU cycles    | 3.7 us | 270,000 IOPS                | 3.3 cores                            | 60 cores                           |

Source: Intel Feb 2015 "Performance Benchmarking for PCIe and NVMe Enterprise Solid-State Drives White Paper

75% of CPU cores used only for IO management !

#ARMTechCon **Cresbar**

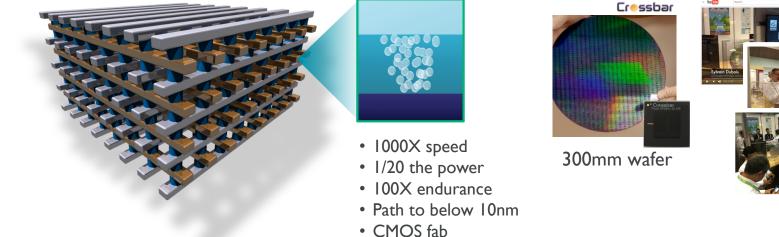

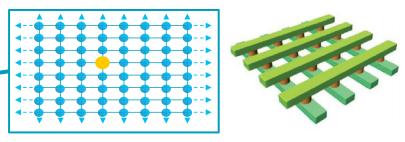

# RRAM revolutionizing NVM technology

### NANO-FILAMENTS ARE THE NEW ELECTRONS

### I<sup>ST</sup> MANUFACTURING PARTNERSHIP WITH SMIC

### **READY FOR LICENSING**

### #ARMTechCon **Cressbar**

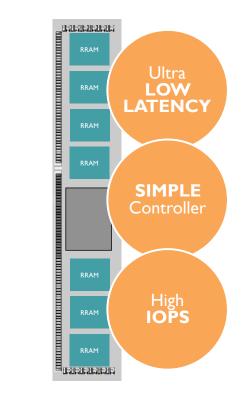

# RRAM unleashing storage solutions performances

- At chip level:

- 100X: Ius random read vs 100s us for 3D TLC NAND

- 1000X: 2us writes vs milliseconds

- At storage level:

•

•

- 4us on NV-DIMM

- IOus on NVMe SSD

- Overwrite capability:

- No erase operation required

- No FTL

- No Garbage Collection

- No Over-provisioning

- High endurance

- Small page support. Almost no performance gap between RD and WR

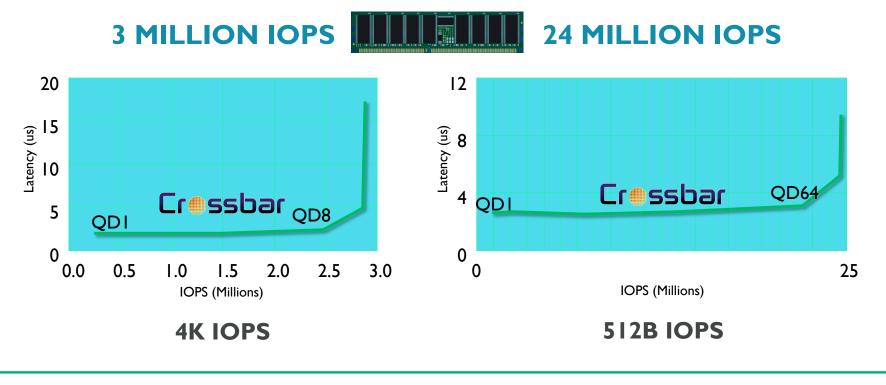

- 24 MIOPS (512B) on a 4TB NV-DIMM (no DRAM, no super caps) 3 MIOPS with 4KB IOs

- 6.4 MIOPS (512B) on a NVMe SSD 800 KIOPS with 4KB IOs

### Unique low latency high density storage solutions

# **RRAM** solving storage latency limitations

Flash PCIe NVMe SSD < 10X latency improvements FS/Driver 20X latency improvements Tread **RRAM PCIe NVMe SSD** NVM Data Tx/RX Link Tx/Rx Misc SSD **RRAM NV-DIMM** 0.0 60.0 80.0 20.0 40.0 100.0 120.0

**RRAM SUPERIOR READ LATENCY (MICROSECONDS)**

Your big data accessible below 5us latencies

#ARMTechCon **Cressbar**

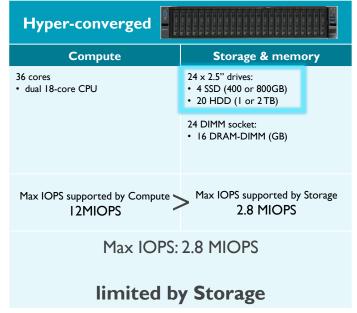

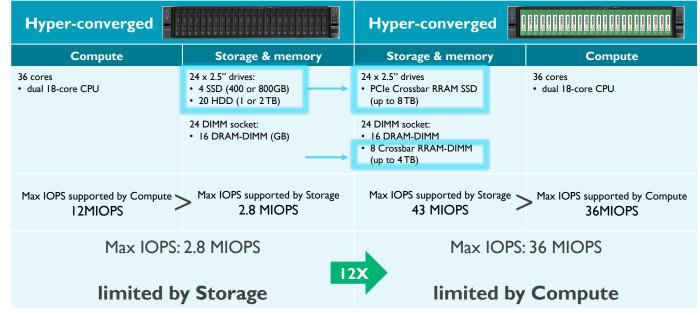

# Performance bottleneck shift from storage to compute in hyperconverged server

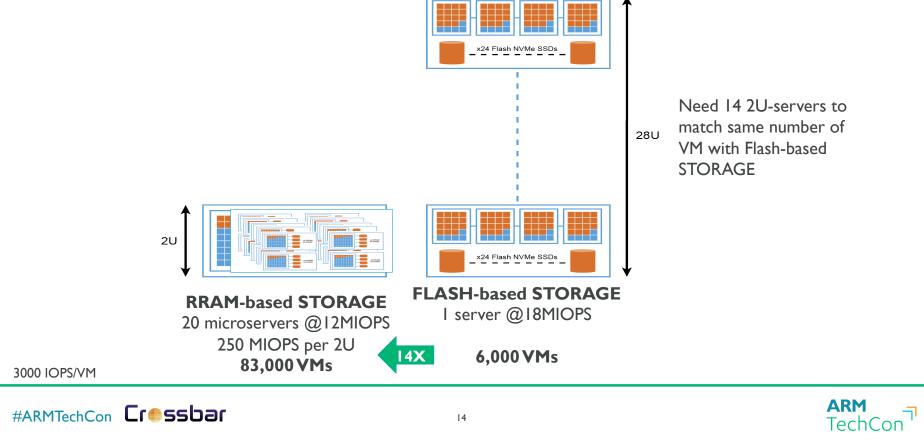

3000 IOPS/VM

#ARMTechCon **Cresbar**

П

# Performance bottleneck shift from storage to compute in hyperconverged server

3000 IOPS/VM

**3D RRAM** moving performance bottleneck from storage to compute

# New era of RRAM-based micro-servers

# 14X more VMs per server with RRAM

# Redefining storage solutions with smaller IO size

# **Delivering GIOPS servers**

|                                             | 4KB IO      | 512B IO   |

|---------------------------------------------|-------------|-----------|

| DIMM IOPS                                   | 3 M         | 24 M      |

| Microserver IOPS<br>(4 DIMMs / microserver) | 12 M        | 96 M      |

| 2U server<br>(20 microserver / 2U)          | 250 MIOPS   | 2 GIOPS   |

| IOPS/U                                      | 125 MIOPS/U | I GIOPS/U |

Performance bottleneck shifted from storage to compute and network

#ARMTechCon **Cressbar**

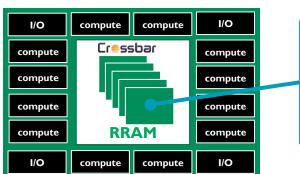

# Next - Enabling new era of computing

Unique memory-centric parallel computing platform

Perfect match for deep neural networks hardware acceleration

#ARMTechCon Cressbar

# Thank you

#ARMTechCon